用智能体设计芯片?我劝你先别高兴的太早

本文来自微信公众号: 老石谈芯 ,作者:老石

这样就不会错过老石的每一篇推送了

先问一个问题:你有没有用过任何AI智能体?

至少在软件开发领域,写代码这件事情好像已经要被硅基生物彻底接管了。软件工程师们一边喊着“药丸”,一边偷偷给自己的IDE装上各种最新的代码助手,对每个大模型和智能体的优缺点如数家珍……

于是,一个非常自然的念头开始在芯片工程师群体中蔓延:

既然智能体能写代码、调Bug、自动跑CI/CD,那能不能也让它来设计芯片?

想象一下,你只需要在对话框里输入一句话:设计一颗3nm的AI加速芯片,功耗300W,性能对标H100。然后,智能体自动调用前端设计工具写RTL,自动跑综合、验证、布局布线、签核,最后吐给你一个GDSII。

还是先别高兴太早。现在幻想用智能体设计芯片,和我当年想到底去北大还是去清华差不多是一个意思。

最主要的原因是,用智能体写软件,和用智能体设计芯片,中间隔着的不是“工具差异”,而是物理世界与抽象世界的鸿沟。

让智能体照方抓药,在EDA里行不通?

很多人对“用智能体做芯片设计”这件事的理解,其实非常朴素:

不就是让一个Agent去调用各种EDA工具吗?

比如,前端Agent负责写RTL,后端Agent负责跑P&R,验证Agent负责看报错,出了问题就多跑几次,直到收敛。

如果你是写软件的,这个逻辑大概率是成立的。

但在EDA领域,这种照方抓药式的智能体思路,很快就会撞上三堵墙。

第一堵墙:芯片设计不是离散问题,而是连续物理优化问题。

现在的大模型都很聪明,它们看过数以亿计的软件代码,所以它们懂逻辑、懂语法。但是,它们不懂物理。

它们不知道当两条金属线靠得太近时会产生串扰(Crosstalk);它们不知道当晶体管密度过高时,局部热点(Hotspot)会导致芯片瞬间熔断。在芯片里,时序、功耗、IR Drop、EM、SI、热……等等等等:它们全部是连续变量,而且高度耦合。

你在某个地方把时序拉回来10ps,可能在另一个地方引入新的功耗热点。

第二堵墙:EDA工具不是优雅的函数,而是经验的黑盒。

很多EDA工具的真正价值,并不在算法本身,而在无数工程经验堆出来的默认参数、启发式策略和corner case,行业黑话叫“know how”。

你可以让Agent调用工具,但你很难让Agent理解:为什么这个warning可以忽略,那个不行?

第三堵墙:责任链断裂。

软件里,AI写的代码出问题,大不了rollback,或者拔电断网。

但芯片流片失败,动辄就是上亿成本。所以问题就来了:谁来为智能体的“自主决策”负责?

这就不是技术问题了,而是工程伦理和产业责任问题。

智能体AI卡在EDA的哪一步?

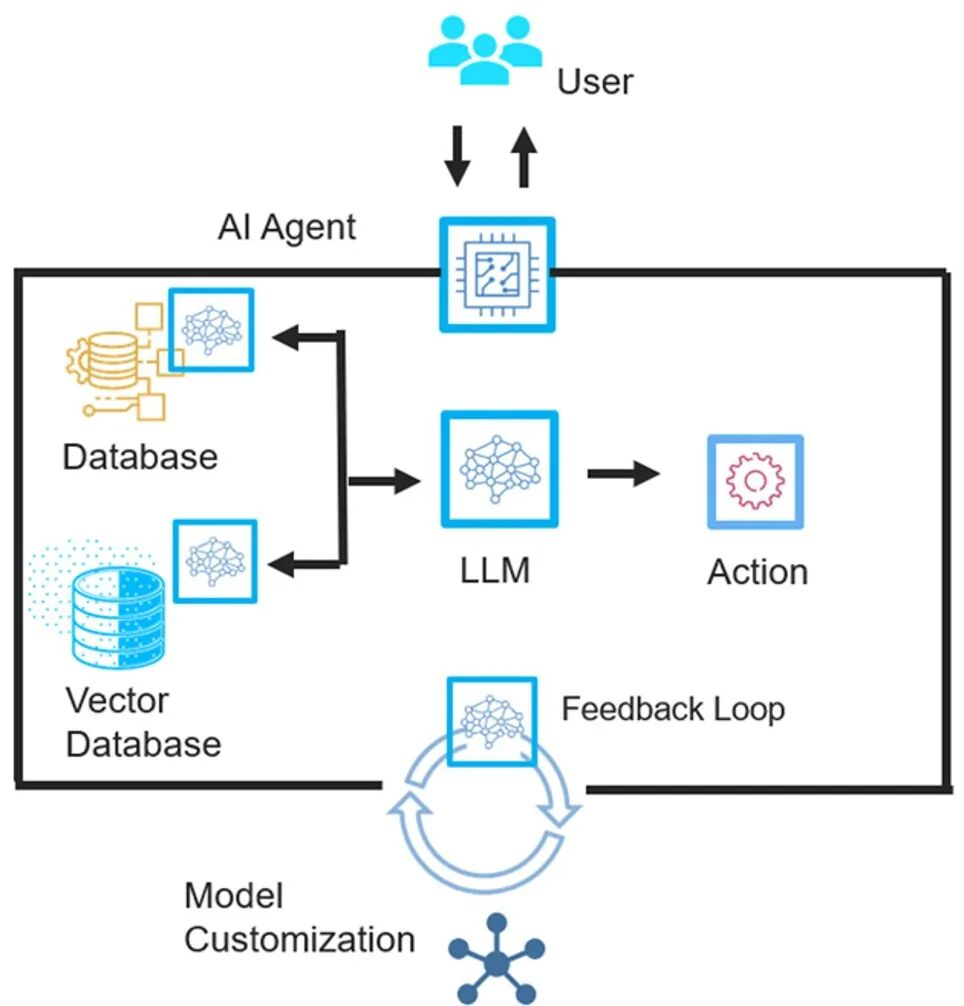

如果我们站在一个更长期的技术演进视角,能看到一个非常关键的事实:智能体AI要真正实现EDA全流程自主设计,目前至少卡在两个核心瓶颈上。

第一,多智能体协同协议严重缺失。

今天绝大多数智能体系统,本质上仍然是单Agent+工具调用,或者多个Agnet的静态分工。但EDA的本质,是一个跨前端、后端、验证、工艺、封装的紧耦合系统。

所以,如果多个Agent之间没有统一的设计意图描述语言、没有冲突检测与调和机制、没有目标对齐协议,那么所谓“多智能体”的美好理想,只会变成:

第二,跨物理场、跨尺度建模能力不足。

芯片设计不是单一物理问题,而是电、热、力、工艺、可靠性等等各种关键参数的的跨场耦合。特别是现在进入后摩尔时代,在先进工艺节点下,量子隧穿、随机工艺波动已经开始影响设计决策。

但如果智能体的决策模型里,没有物理机理,只靠历史数据拟合,那它做的不是设计,而是赌博。

智能体设计芯片,到底还有没有未来?

提到前面的那些问题很多人第一反应是,是不是模型还不够大?数据还不够多?

但在EDA领域,更大的模型并不总是关键解法。观察现在的技术发展与卡点,能看到真正的技术攻坚方向,其实只有两个:

方向一,把芯片物理机理嵌入智能体的决策框架。

这意味着不只是用AI预测结果,而是让AI理解为什么不能这么做。比如,让智能体AI有理有据的回答这些问题:为什么这个buffer不能再插?为什么这个局部拥塞不是靠reroute能解决?

本质上来说,这是一个可解释自主优化的问题,而不是寄希望于黑盒拟合来实现。

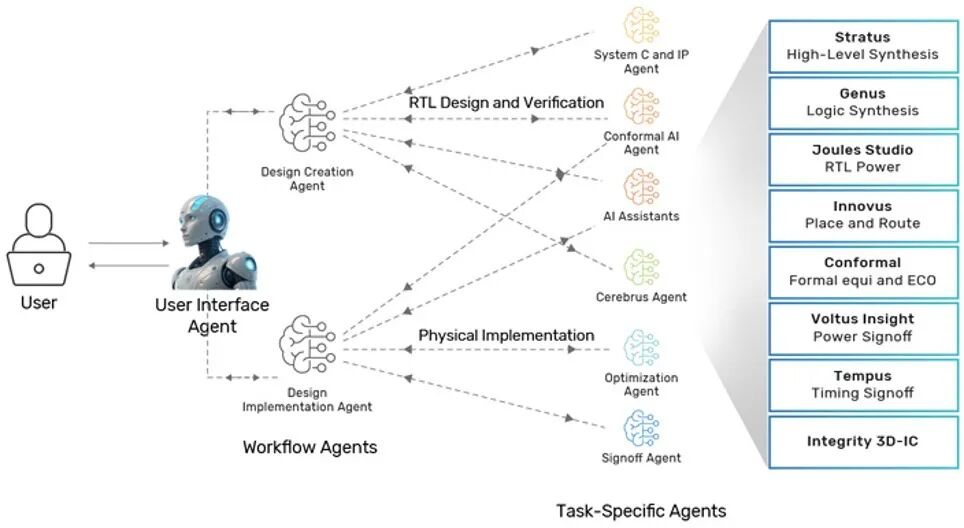

方向二,构建动态编排的多智能体协同协议。

真正可用的EDA智能体系统,不应该是你负责前端,我负责后端,互不干扰;而应该是,当某个区域出现时序瓶颈时,前端、后端、验证Agent能动态调整协作边界,并围绕问题临时形成“任务联盟”。正所谓:聚是一团火,散是满天星。

EDA需要迎接一场底层逻辑重构?

这还没完。如果说先进工艺节点让EDA变的更难,那么Chiplet和异构封装,则是让EDA变了一个物种。

在Chiplet时代,设计不再是一块芯片die的PPA优化,而是多Die、多工艺、多协议、多封装层级的系统级权衡。

这对智能体AI提出了一个非常苛刻的要求:它必须从工具级辅助,进化为系统级自主规划。

这意味着EDA工具链不能再各自为战、先分模块再返工;正相反,构建EDA的底层逻辑可能就需要被重构为以下三层:

顶层:系统级目标分解与约束生成

中层:跨模块、跨Chiplet的协同优化

底层:具体工具的自主参数适配

智能体AI在EDA的落地路线图:别一步跨太大

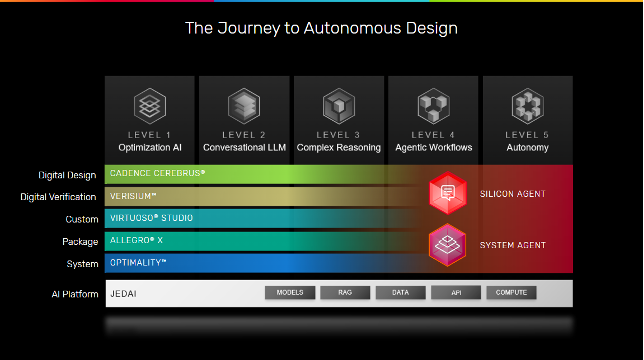

如果我们借鉴自动驾驶的分级体系,其实可以把EDA智能体能力分成五个阶段:

L1:优化型AI(今天已大量商用)

L2:对话式AI(提升工程师效率)

L3:推理+DSL生成(自动脚本与流程拼装)

L4:工作流级智能体(模块级自主设计)

L5:全流程自主设计(长期研究目标)

现实的落地路径,注定是从低到高。真正理性的行业路线,应该遵循“三步走”:

第一步,场景穿透。即优先选择高痛点、低风险场景,比如:DRC自动修复、局部时序优化、Chiplet链路约束探索等等。先把低处的果子摘了。

第二步,能力沉淀。即把单点成功经验,沉淀为多智能体协同平台,逐步实现模块级的自主设计闭环。

第三步,范式重构。当技术、责任、生态逐渐成熟,EDA才有可能真正进入“设计能力服务化”的新阶段。

EDA公司在智能体这条路上,走到哪了?

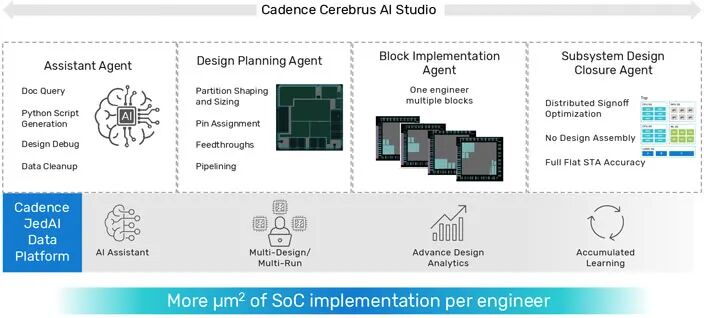

以Cadence举例,它是目前EDA巨头中对智能体方向布局比较系统且克制的一家。

他们并没有急着喊“全自动设计芯片”,而是非常清楚地选择了从工具级AI,向系统级Agent逐步演进。

比如,为了让AI理解物理规则,Cadence的数字后端工具Cerebrus并不是简单地用神经网络去预测布局,而是采用了一种强化学习的架构。它会不断地尝试各种布局规划和参数配置。每尝试一次,底层的EDA引擎(比如Innovus)就会基于真实的物理模型,进行一次快速的评估(Reward/Penalty),并告诉AI这步走得好、功耗降了5%;或者这步不行,导致了严重的拥塞。

这个过程,不再是黑盒的“盲猜”,而是物理约束下的自主优化。

更进一步,到了Optimality这种针对多物理场系统仿真的工具中,AI面对的挑战升级了。这里不仅有电,还有热,还有磁。

在传统流程里,做一次全系统的电磁仿真可能需要几天。Optimality的做法是利用AI学习物理场的分布规律,用“AI代理模型”来加速求解过程。但请注意,这里的AI不是凭空捏造数据,而是基于麦克斯韦方程组的边界条件进行训练的。这说明智能体AI要想接管EDA,必须实现物理机理与自主决策的深度融合。它不能只看数据(Data-Driven),必须同时看规则(Physics-Driven)。

Cadence还花大力气搞了JedAI Platform,它把Cadence全家桶(Verification,Implementation,Analog,PCB,System)产生的所有数据,全部清洗、统一格式,存入一个巨大的数据湖中。这样他们的验证智能体Verisium就可以读取Cerebrus的历史数据,分析哪些模块最容易出Bug,从而针对性地生成测试用例。而系统优化智能体Optimality可以把散热数据实时反馈给Virtuoso,指导电路版图设计。

从这些例子可以看出,Cadence的路线非常清晰:

先解决真实痛点,再谈范式重构。

这也是为什么他们现在的AI,大多仍然停留在“可控的智能增强”,而不是“放飞自我”的自治系统。

写在最后:别指望智能体替你背锅

智能体一定会深刻改变芯片设计,AI一定会深刻改变芯片设计。这我毫不怀疑。

但它改变的方式,或许不是直接取代工程师,而是让工程师不断升级认知、推动EDA工具重构底层逻辑,并迫使整个行业重新思考责任与边界。

所以,当你听到有人说:再过两年,AI就能全自动设计芯片了。

你可以报以礼貌的微笑。

然后继续把自己的基本功练扎实。

因为你知道,在很长一段时间里,智能体可以帮你加速,但没办法替你背锅。

。